장효과 트랜지스터

장효과 트랜지스터 또는 전계효과 트랜지스터(field effect transistor, 약자 FET)는 게이트 전극에 전압을 걸어 채널의 전기장에 의하여 전자 또는 양공이 흐르는 관문(게이트)이 생기게 하는 원리로 소스, 드레인의 전류를 제어하는 트랜지스터이다. 트랜지스터의 분류 상 바이폴라 트랜지스터와 대비되어 단극 트랜지스터(unipolar transistor)로 분류된다.

장효과 트랜지스터는 게이트 아래에 놓인 절연층에 의해 축전기 구조가 형성되므로, 공지층에 의한 유사 교류 축전기만을 가지는 접합형 트랜지스터에 비해 동작 속도가 느리고 전송 컨덕턴스(gm)가 낮다는 문제가 있지만 게이트 전류가 거의 0인 장점이 있고 구조가 긴요해서 접합형 트랜지스터보다 고밀도 집적에 적절하므로 현대의 집적 회로에 주류가 되고 있으며, 논리 회로 소자의 집적 회로 외에 아날로그 스위치/전자 볼륨에도 응용된다. 극초단파이상에서는 규소보다 캐리어의 이동도가 빠른 갈륨 비소(GaAs)와 같은 화합물 반도체를 이용한 FET가 사용되고 있다.

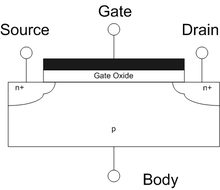

금속 산화물 반도체 장효과 트랜지스터 (MOSFET) 편집

4단자형(MOS(metal–oxide–semiconductor)형)에서는 각각의 단자를 소스(source), 게이트(gate), 드레인(drain), 백 게이트(back gate)(혹은 벌크), 3단자 FET의 경우는 소스, 게이트, 드레인이라고 부른다. 대칭형 소자이기 때문에 소스와 드레인에 구조적인 차이는 없고 단지 전압을 인가했을 때에 두 단자를 비교했을 때, n형이면 고전압쪽을 드레인, 저전압쪽을 소스이고 p형이면 그 역이 된다.[1][2] 아래처럼 소재, 문턱 전압에 의해서 구별되는 다양한 종류의 전계효과 트랜지스터가 존재하지만 현재 가장 넓게 사용되고 있는 것은 실리콘을 사용한 향상 MOS형(이하 MOS라고 표기)이므로, 특별한 언급이 없는 경우는 전계효과 트랜지스터는 실리콘 MOS(Si CMOS)를 가리키는 것으로 한다.

MOSFET의 동작 편집

이론적으로 n형과 p형의 차이는 드레인-소스간의 전류에 기여하는 캐리어의 차이 뿐이므로 여기에서는 n형에 대해서만 취급한다.

MOSFET에서는 게이트와 기판(substrate) 사이에 구성된 축전기에 의하여 게이트 정전압이 인가되었을 경우 p형 기판과 절연층의 경계면에 전자를 끌어들여 드레인-소스사이에 반전층(n형)을 만들어내는 일로 소스-드레인사이를 고컨덕턴스가 되게 한다. 드레인-소스간 전압이 비교적 낮고 게이트-드레인사이의 전압이 문턱 전압을 넘은 상태; 즉 게이트-소스 전압에서 문턱 전압을 뺀 값보다 낮은 상태이며 반전층이 드레인-소스사이에 걸려서 마치 저항같은 기능을 가지게되며 이를 선형 영역이라고 부른다.

선형 영역에서는 게이트 전압에 비례해서 반전층 두께가 더해져서 컨덕턴스가 게이트 전압에 비례해서 증가된다. 한편 게이트-드레인간 전압이 문턱 전압보다 밑돌게 되면 드레인 영역 부근에서 반전층이 형성되지 않게 된다.(게이트-드레인간 전압이 문턱 전압이 된 상태를 핀치 오프라고 불림) 이 상태(핀치 오프)를 포화 영역이라고 부르며, MOS 컨덕턴스는 반전층의 길이에 의해서 일정하게 된다.

이 상태에서 정전류원으로 다루어진다. 반전층의 길이는 게이트-드레인 전압에 의해서 그 후에도 계속 바뀌기 때문에 컨덕턴스도 이것을 따라서 변화한다. 이를 채널장 변조 효과라고 부르며 접합형 트랜지스터의 어리 효과에 대응된다.

전력 MOSFET 편집

MOSFET의 내부가 큰전력의 스위칭용으로 설계된 것이다. 양극성 전력 트랜지스터와 비교해서 전압 구동형 소자이기 때문에 구동 회로의 전력 소비가 낮다. 그리고 다수 캐리어 디바이스이며 본질적으로 고속 스위칭이 가능하고 스위칭 손실도 적다. 그러나 내압이 높아질 경우에 온 저항이 높아지는 문제점이 있다.

2000년대가 되어서 트렌치 게이트, 의평면 접합같은 구조의 모색으로 인하여 고내전압화, 언 저항, 스위칭 손실의 감소를 동시에 만족시키는 것도 개발되었다. 게다가 2006년 기준으로는 초접합 구조를 이용해 실리콘의 이론적 한계를 넘어서는 저손실의 것도 개발되고 있다.

성질 편집

전기적 특성을 보여주는 모든 특성(대신호) 편집

드레인-소스 전압(이하 Vds), 게이트-소스 전압(이하 Vgs), 문턱 전압(이하 Vt)라고 할 때 MOS의 동작 영역은 크게 4가지로 나뉜다.

- 차단 상태: :

- 선형 상태:

- 포화 상태:

- 브레이크다운:

- :브레이크다운 전압

각각에서 드레인 전류 는 아래와 같이 이론식(실험식이 아님)을 만족한다.

- 차단 상태:

- 선형 상태:

- 포화 상태:

- 브레이크다운:

주요 원인의 현상이 다르지만 일반적으로 소자 파괴에 이르기까지 전류가 증가할 때를 다룬다.

- : n형 MOS의 경우

- : p형 MOS의 경우

- : 단위 면적 주위의 게이트 산화막 크기

- : 전자 이동도

- : 양공 이동도

- : 채널장 변장 계수

전기적 특성을 보여주는 모든 특성 (소신호) 편집

소신호 특성은 등가 회로에 규정된 각 매개변수가 아래와 같은 식을 만족한다.

- : 오버랩 전기 용량

- : 접합 용량

- 는 고유 용량(intrinsic capacitance)을 표시하며, 그 값은 동작 영역에 의해 아래처럼 변화한다.

차단 영역:

선형 영역:

포화 영역:

종류 편집

게이트 접합부의 구조에 의한 분류 편집

- 금속 산화막 반도체형(metal oxide semiconductor FET, MOSFET): 게이트 부분이 반도체의 산화 피막상의 금속 전극이 되어 있는 것이다. 현재의 집적 회로의 주류가 되고 있는 소자이며 p/n 모두 같은 형태를 가지는 회로의 경우에는 양형을 모아서 CMOS형(상보형 MOS, Complementary MOS)이라고 부른다.

- 접합형(Junction FET, JFET): 게이트 부분이 보통 트랜지스터와 동일하게 이종 반도체의 접합면이 되어 있는 것이다. MOS와 동작 원리가 달라서 접합면에 생기는 공지층에 의하여 전류를 제어한다.

- 금속 반도체형(Metal Semiconductor FET, MESFET): 게이트 부분이 금속 전극과 반도체에 집적 접합되어 있는 것이다.

게이트 전압과 드레인 전류에 의한 분류 편집

- 인핸스먼트형(enhancement type) = 노멀리 오프형 (normally off type) : 게이트 전압을 걸지 않을 때 채널이 존재하지 않고 드레인 전류가 흐르지 않는 것이다.

- 디플리션형(depletion type) = 노멀리 온형 (normally on type) : 게이트 전압을 걸지 않을 때 채널이 존재해서 드레인 전류가 흐르는 것이다.

채널의 극성에 의한 분류 편집

트랜지스터에 PNP형과 NPN형이 있듯이 FET에도 p채널형과 n채널형이 있다.

MOS에는 기본적으로 소스, 드레인 단자에 금속(알루미늄같은 배선층)을 접합한다. 이때 접촉 저항을 내리는 목적으로 비교적 높은 농도의 불순물을 넣는다. 불순물이 n형(p형 실리콘 기판에서 III값의 물질(B : 붕소 등))의 경우는 n+형(n웰)으로 불리고, 불순물이 p형(n형 실리콘 기판에서 V값의 물질(P : 인 등))의 경우에는 p+형(p웰)으로 불린다.

불순물을 포함시키지 않고도 접촉 저항이 충분히 낮은 경우는 불순물을 넣을 필요가 없어서 p, n 어느 쪽에도 속하지 않는다. 이것을 언바이폴러 트랜지스터라고 불린다. 이 소자는 게이트에 마이너스 전압 (소스로부터)을 가하거나 플러스 전압을 가해도 문턱 전압 이상이면 전류를 흘린다.

1980년대 중순까지 메모리 IC나 논리 IC는 그 당시 집적 기술의 문제때문에 p, n 양쪽 모두를 제조하는 것이 어려웠기 때문에 저항에서 CMOS의 한쪽 편을 대신한 p-MOS, n-MOS가 이용되었다. 처음 제품이 나왔을 때는 제조가 쉬었던 p-MOS가 주력이었지만, 이후에는 이동 속도가 빠른 전자 캐리어를 가지는 n-MOS가 주력이 되었다.

1980년대 초에는 표준 논리 IC가 시모스구조로 만들어졌다. 1990년대에는 전기적 특성이 아날로그의 실제 레벨에 도달한 것과 시스템 LSI같은 논리 회로와 아날로그 회로가 섞여서 집적된 관계로 아날로그 회로도 시모스로 제작되게 되었다.

제품 번호 편집

일본에 있어서 FET의 제품번호는

- 2SJxxx P채널 FET

- 2SKxxx N채널 FET

처럼 번호를 붙이는 것이 많다. 혼합 (주파수 변환), 이득 조정의 목적으로 2개의 게이트를 가지는 품목이 있고 이 경우는 3으로 시작되는 번호를 붙일 수 있다. 제조사에 따라서 전류, 정격 전압의 분류에 따라서 독자적인 제품번호를 붙이는 경우도 있다.

정전류 다이오드 편집

JFET는 『게이트 전압이 일정하면 드레인 전류가 일정』라는 성질을 가지기 때문에 회로에 직렬로 연결하면 항상 일정한 전류가 흐르는 정전류 소자로 사용할 수 있다. 이것을 하나의 전자 부품으로 사용한 것을 정전류 다이오드라고 불린다. 다이오드의 이름이 붙어 있지만 구조는 완전히 다르다.

같이 보기 편집

- CMOS (상보성 금속 산화막 반도체)

참고 문헌 편집

- 최신 전계효과 트랜지스터 (FET) 규격표 각년도판 (CQ 출판사)

- 1968년판(초판)에서 1986년판까지는 개별 특성 그림이 붙여 있다.

- 1987년판부터는 개별 특성 그림이 생략되었다.

- 1994년판부터는 초기의 FET 규격이 생략되었다.